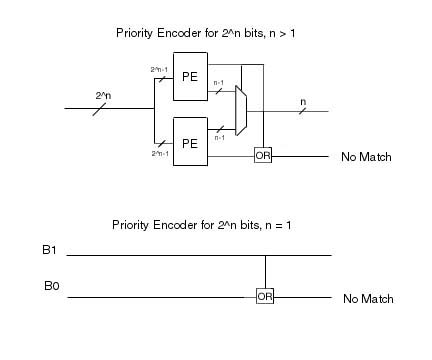

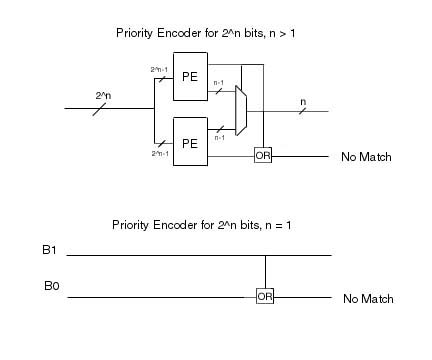

Priority Encoder:

VLSI LAyout

IR SIM Simulation

Cazm Simulation of priority encoder

Information:

The priority encoder is very unique device. Not only can it determine which active match-line has the highest rank or "priority," but it will also translate the memory location of that match line into binary.

Specs:

Speed: 15ns

Size: 600 x 822 lambda

# transistors: 294

# drawn trans: 36

replication factor: 8x

active area vs. routing area: 24356/464992 = 5.24%

total area/block: 489348 lambda sq.

area vs # trans: 42.75 lambda sq / tran.

power consumption: 48 E -12 W

design time: n/a

Modifications:

None.

Downloads:

Priority Encoder Layout

Copyright(c) 2000 Brian Magnuson